### 半導体 pn接合

## 金属一半導体一絶縁体

金属と半導体の間には明確な区別が存在する。しかし、半導体と絶縁体は、基本的に同じ範疇にあるが、電気伝導度の大雑把な大きさの違いで区別している。

金属の定義とは、フェルミ面が存在すること、すなわち、フェルミ準位に有限の状態密度が存在することである。それに対し、半導体、絶縁体はフェルミ面を持たず、フェルミ準位はエネルギーギャップ内に位置する。

# 真性半導体

半導体とは、明確な境界は無いが、室温における電気抵抗率 $\rho$ が $10^{10}\sim0.01\Omega$ /cm 程度に属する絶縁体をさす。半導体の代表的な元素として、Si, Ge が良く知られている。数種の半導体におけるエネルギーギャップの大きさを、右の表に示す。絶対零度においては、半導体の価電子帯は完全に充満し、且つ、伝導帯は空であるため、電気伝導度はゼロになる。有限温度では、価電子帯から伝導帯に熱励起された電子一正孔対が電荷を運ぶ担体になる。室温では、こう

表 1 種々の半導体のエネルギーギャップ

|         | Energy Gap |  |  |  |  |

|---------|------------|--|--|--|--|

| Diamond | 5.4 eV     |  |  |  |  |

| Si      | 1.11 eV    |  |  |  |  |

| Ge      | 0.66 eV    |  |  |  |  |

| GaAs    | 1.43 eV    |  |  |  |  |

| CdS     | 2.42 eV    |  |  |  |  |

|         |            |  |  |  |  |

して生成された電荷担体のみが伝導度を担っており、真性半導体と呼ばれる.

#### 半導体の自由キャリア(電荷担体)密度

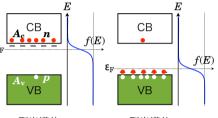

有限温度における半導体中を自由に運動できる電荷担体密度は、図1のようにフェルミーディラック分布で支配される。

$f(E) = 1/(e^{(E-E_F)/k_BT} + 1)$  (1)

この時に表1に見られるように、エネルギーギャップ  $E_g$  は温度  $k_BT$  よりも十分に大きいので、(1) 式はMaxwell-Boltzmann 分布で近似できる。伝導帯( $f_C(E)$ )と荷電子帯( $f_V(E)$ )についてそれぞれ

$\epsilon_{\mathrm{F}}$  VB

$$f_{\rm C}(E) \approx e^{-(E-E_{\rm F})/k_{\rm B}T}$$

$$= e^{-(E_{C}-E_{F})/k_{B}T} e^{-(E-E_{C})/k_{B}T}$$

(2a)

$f_{V}(E) = 1 - f(E) \approx e^{(E-E_F)/k_BT}$  $= e^{(E_V-E_F)/k_BT} e^{(E-E_V)/k_BT}$

(2b)

と表現できる。伝導帯の電荷担体密度は、その状態密度 D(E) を用いて、

$$n_{\rm C} = \int_{E_{\rm C}}^{\infty} f_{\rm C}(E) D(E) dE = \int_{E_{\rm C}}^{\infty} D(E) e^{-(E - E_{\rm C})/k_{\rm B}T} dE e^{-(E_{\rm C} - E_{\rm F})/k_{\rm B}T}$$

(3)

で与えられる。伝導帯のエネルギー分散を  $E(k)=E_{\rm C}+(\hbar k)^2/2m^*$ 、3次元系の単位体積あたりの状態密度として  $D(E)=(1/2\pi^2)(2m^*/\hbar^2)^{3/2}$  ( $E\!-\!E_{\rm C}$ ) $^{1/2}$  を用いると、電荷担体密度  $n_{\rm C}$  は  $n_{\rm C}=2(m^*kT/2\pi\hbar^2)^{3/2}$   $e^{-(E_{\rm C}\cdot E_{\rm F})/k_{\rm B}T}=2(2\pi m^*kT)^{3/2}/\hbar^3$   $e^{-(E_{\rm C}\cdot E_{\rm F})/k_{\rm B}T}=A_{\rm C}$   $e^{-(E_{\rm C}\cdot E_{\rm F})/k_{\rm B}T}$  (4) と得られる。

3次元状態密度

$(2m^*(E-E_C))^{1/2}/\hbar = k = (6\pi^2N/V)^{1/3}$

これをn = N/V について解き、

$n = (2m^*(E-E_C))^{3/2}/6\pi^2\hbar^3$

これをエネルギーで微分して単位体積あたりの状態密度 D(E) を得る:

$D(E) = 2 dn/dE = (1/2\pi^2)(2m^*/\hbar^2)^{3/2} (E-E_C)^{1/2}$ ,

ここで、因子2はスピンの自由度から来る。

エネルギー積分  $\int_{E_{\rm C}}^{\infty} (E\!-\!E_{\rm C})^{1/2} \, e^{-(E\!-\!E_{\rm C})a} \, {\rm d}E$   $t^2\!=\!E\!-\!E_{\rm C}$ 、 ${\rm d}E/{\rm d}t = 2t$  と置くと、  $= \int_0^{\infty} t \, e^{-t^2a} \, 2t \, {\rm d}t = 2 \int_0^{\infty} t^2 \, e^{-t^2a} \, {\rm d}t = (1/2)(\pi/a^3)^{1/2}$  を得る。

## 不純物半導体

通常、半導体素子として使用されるのは、不純物ドーピングにより電荷担体を導入した不純物半導体である。大きく2種に分けられ、4価の Si や Ge より価数が 1 つ多い P, As, Sb などの電子供与体をドープした、電子が電荷担体の n 型半導体と、価数が1つ少ない不純物 B, Al, Ga, In などの電子受容体をドープした p 型半導体がある。

ドープされた不純物の電子や正孔の軌道半径およびイオン化ポテンシャルは、 $\mathrm{Si}$  や  $\mathrm{Ge}$  結晶内の遮蔽効果とバンドの形で決まる小さな有効質量  $m^*$  に支配されている。電子の運動エネルギーは

が最小になるドナー電子軌道半径  $a_{\rm D}$ を取る:  $\partial E/\partial a=-\hbar^2/(m^*a_{\rm D}^3)+e^2/\epsilon a_{\rm D}^2=0$  より

$a_{\rm D} = \varepsilon \hbar^2 / (m^* e^2) = a_{\rm H} \varepsilon m_0 / m^* = 0.529 \varepsilon m_0 / m^*.$  (Å) (5)

電子や正孔が不純物原子から離脱する際に必要なイオン化エネルギーは、運動エネルギーからポテンシャルエネルギーを差し引いて得られる:

$$E_{\rm D} = e^2/2\epsilon a_{\rm D} - e^2/\epsilon a_{\rm D} = -e^2/2\epsilon a_{\rm D} = E_{\rm H}a_{\rm H}/\epsilon a_{\rm D} = E_{\rm H}m^*/m_0\epsilon^2.$$

(6)

09/12/15 09/12/15

#### 軌道半径とイオン化エネルギー

Si と Ge の場合について、右表の誘電率 $\epsilon$ と有効質量  $m^*$  を用いてドナー電子の軌道半径とイオン化エネルギーを求めよう。軌道半径  $a_{\rm D}$  は  $\epsilon m_0/m^*$  に比例するので、水素原子のBohr半径  $a_{\rm H}$

|    | 8    | m*/m <sub>0</sub> | ε <i>m</i> <sub>0</sub> / <i>m</i> * | $a_{ m D}$ (Å) | $E_{\mathrm{D}}=E_{\mathrm{H}}a_{\mathrm{H}}/\epsilon a_{\mathrm{D}}$ $(\mathrm{eV})$ |

|----|------|-------------------|--------------------------------------|----------------|---------------------------------------------------------------------------------------|

| Ge | 15.8 | 1/5               | 79                                   | 41.8           | 0.011                                                                                 |

| Si | 11.7 | 1/2               | 23.4                                 | 12.4           | 0.05                                                                                  |

表 2

$=0.529\,\mathrm{\AA}$  に右表の数値を掛けて得られる。一方、イオン化エネルギーは  $1/\epsilon a_\mathrm{D}$ に比例するので、水素の $1\mathrm{s}$ 軌道のイオン化エネルギー  $13.6\,\mathrm{eV}$ に掛けると右表の数値が得られる。 半導体中の不純物準位は、この小さなイオン化エネルギー分だけ荷電子帯、或いは伝導体から離れたエネルギーギャップ内に位置する。

## エネルギー準位

不純物半導体のエネルギー準位を図3に $E_F$ 示す。通常、電子数密度nとホール数密度pは非常に小さいために、伝導体下端 $E_C$ と荷電子帯上端 $E_V$ は $E_C$ と荷電子帯上端 $E_V$ は $E_C$ が $E_D$ が $E_D$ が $E_D$ が、その

n 型半導体 図3 p 型半導体

ため (1) のFermi-Dirac 分布関数はボルツマン因子  $e^{-(E_C-E_F)/k_BT}$  および  $e^{-(E_F-E_V)/k_BT}$  で良く近似される。その結果、n と p の間にはエネルギーギャップのみに依存する半導体方程式(質量作用の法則とも呼ばれる)が成り立つ:

$$np = A_{\rm C} e^{-(E_{\rm C} - E_{\rm F})/k_{\rm B}T} A_{\rm V} e^{-(E_{\rm F} - E_{\rm V})/k_{\rm B}T} = A_{\rm C} A_{\rm V} e^{-E_{\rm g}/k_{\rm B}T}.$$

(7)

ここで、 $A_{\rm V}$  (=  $2(2\pi m^*kT)^{3/2}/h^3$ ) は荷電子帯の有効状態密度、 $A_{\rm C}$ は伝導帯の有効状態密度である。この関係式は、真性半導体でも成り立つことは自明であろう。

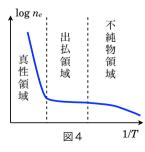

図4に、不純物半導体の電荷担体密度 ne の模式的な温度 (1/T) 依存性を示す。

- 1) **不純物領域**:  $k_{\rm B}T < E_{\rm Ion}$ :不純物のイオン化エネルギー  $E_{\rm Ion}$  以下の低温領域を指し、担体密度はボルツマン因子  $e^{-E_{\rm Ion}/k_{\rm B}T}$  にしたがって増加する。

- 2) 出払領域:  $k_BT \ge E_{\text{Ion}}$ : 温度がイオン化エネルギーと同程度、或いはそれ以上の高温領域を指し、不純物がほぼ完全にイオン化し、温度によらず担体密度は一定になる。

- 3) **真性領域**: $k_{\rm B}T \ge E_{\rm g}$ :熱エネルギーがエネルギー ギャップ以上になると真性半導体と同様に、指数関数的に 担体密度が増加する。

Si や Ge ではイオン化エネルギーが  $0.05~{\rm eV}$  以下なので、常温では出払領域に相当する。

#### 半導体の電気伝導

不純物半導体は、常温では出払領域にあるので金属と似ているが、1)担体数が少ない点、2)担体として電子とホールの2種がある点が異なる。担体の運動エネルギーは、金属のフェルミエネルギー  $E_F$  に対して  $k_BT$  程度と数桁小さいため、小さな波数のフォノンも散乱に効果的に寄与し、電気抵抗は、低温領域まで温度に比例する。

電流密度 j は電子担体とホール担体の和として、

$j = -n_c e < v_c > + n_v e < v_v >$

で与えられる。担体が時間Tの指数関数で記憶を失うとすると、運動方程式は、

$m_c^* a = -eE - m_c^* v_c \hbar$

と書ける。平衡状態では、 $\alpha = 0$  なので平均速度  $\langle v_c \rangle$  は

$<\!\!v_{c}\!\!> = -eE \tau_{\!c}/m_{c}^{*} = -\mu_{c}E$

$<\!\!v_{\rm v}\!\!> = eE \tau_{\! {\rm v}}/m_{\rm v}^* = \mu_{\rm v} E$

となる。ここで、 $\mu_i = e \pi / m_i^*$  は担体 i の移動度( $cm^{3/2}$   $g^{-1/2}$ , (cgs)、  $cm^2$ /volt/s(良く見かけるが混合単位)。従って、電気伝導度 $\sigma$ (1/s, (cgs))は

$\sigma = j/E = n_c e^2 \tau_c / m_c^* + n_v e^2 \tau_v / m_v^*$

と表せる。auは衝突間隔で、平均自由行程 $au_{pt}$ と速度vの比、 $au_{pt}/v$ で書ける。 $au_{pt}$ は、温度に比例して増加するフォノン数の逆数、1/Tに比例し、vは運動(熱)エネルギーの平方根、 $1/T^{-1/2}$ に比例するため、

$\tau_{ph} \propto T^{-3/2}$

で与えられる。

一方、低温領域では不純物散乱が効いてくる。温度降下と共に電荷担体数が減少するため、不純物ポテンシャルの遮蔽効果が効かなくなり、長距離力になる。

09/12/15 09/12/15

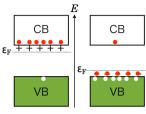

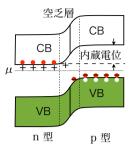

### p-n 接合

アクセプターをドープした p-型半導体と、ドナードープの n-型半導体を接合することに より、整流機能を持たせたりトランジスタの機能発現の素子を構成できる。

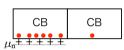

図5の様に、p-型半導体とn-型半導体を考えよう。この 図の横軸は、半導体の長さ方向の位置を表し、縦軸は、 い合う面を接合させて作る。図6は接合させた瞬間を表 している。破線のケミカルポテンシャル $\mu$ (T=0 では Fermi energy) が両側で差が存在する点に注意する。 u は、電子が詰まっているエネルギーの目安であり、食い 違ったuは電子の移動を促す。n-型からp-型半導体に電子 が流れ込み、p-型から n-型にはホールが流れ込む。p-n の 接合界面近辺で両者は対消滅をする。そうすると、ドーパン ト・イオンと共に中性を保っていた電子やホールが消滅する ため、ドナーの正イオンとアクセプターの負イオンが界面に現 (1, 土土土土土 れてくる(この電荷担体が消滅した領域を**空乏層**と呼ぶ)。平 衡状態では、p-n 接合界面の正負の電荷層が作る内部電場のた めに化学ポテンシャルの差 μールが打ち消される。この接合形 成に伴う内部電場を**内蔵電位** Vint 或いは**障壁電位**と呼ぶ。外 部電圧がゼロの時は化学ポテンシャルが場所に依らないため n-型とp-型の接合界面には正味の電流は流れないが、外部電位 を加えると化学ポテンシャルが場所により変化するため、電 荷担体の移動、すなわち電流が流れる。

# 内蔵(障壁)電位

ここで、界面電荷による内蔵電位を図8の様に考察する。

- 1) 空乏層に現れたドーパントの電荷:n-型は正で p-型は負

- 2) 電荷 $\rho = -eN_A = eN_D$  が作る電場は div  $E = \rho/\epsilon$  を積分し て得られる:  $E = \rho(W/2-|x|)/\epsilon(W$  は空乏層の幅)

- 3) ポテンシャル Vと電場 E の負電荷に対する関係式 E= $\partial V/\partial x$ より電位  $V(x)=\rho(Wx-\operatorname{sgn}(x)x^2+W^2/4)/2\epsilon$  が求まる。 従って、内蔵電位

$V_{\rm int} = \rho W^2/4\epsilon$

が得られる。

外部電位  $V_{\text{ext}}$  は主に空乏層に掛かり、それを打ち消すため に空乏層の幅 W が変化する。

$V_{\text{ext}}+V_{\text{int}}=\rho W^2/4\epsilon$

より、空乏層の幅 W は

n 型半導体

図 5

p 型半導体

n 型 ρ型

図6 p型とn型の半導 体を接合させた瞬間。 両者の化学ポテンシャ ルが一致していない。

内蔵電位発生機構 図8

09/12/15

$W = [4\epsilon(V_{\text{ext}} + V_{\text{int}})/\rho]^{1/2} = (4\epsilon V_{\text{ext}}/\rho + W_0^2)^{1/2}$ (8) で与えられる。ここで、 $W_0 = 2(\epsilon V_{\rm int}/\rho)^{1/2}$ 。

## 接合を流れる正味の雷流

n型半導体の電子とp型半導体のホールは、接合界面 を通して2種の電流を生じる。

- 1) 内蔵電位 Vint を乗り越えるためには熱励起の助けが 必要だが、ボルツマン因子  $e^{-eV_{int}/k_BT}$  の確率で電子は p 型 の伝導帯に、ホールは n型の荷電子帯に乗り越え拡散 し、拡散電流  $I_{\text{diff}} \sim e^{-eV_{\text{int}}/k_{\text{B}}T}$  を生じる。

- 2) n型、p型のそれぞれの半導体中で、 $E_{\sigma}$ の熱励起に 内蔵(障壁)電位。 よる電子一ホール対生成がボルツマン因子  $e^{-Eg/k_{\rm B}T}$  の確率 で発生する。それらの電荷担体は、内蔵電位  $V_{int}$  で加速さ れ(電子。ホールはバブルのように昇る)、ドリフト電流 Idrift を生じる。

uは場所に依らないので、これらの電流はちょうど釣り合 い、接合を通過する正味の電流はゼロである。

$I_{\text{drift}} \propto I_{\text{drift}}^0 e^{-Eg/2k_BT} = I_{\text{diff}} = I_{\text{diff}}^0 e^{-eV_{\text{int}}/k_BT}$ . (9)

ここで、 $I^0_{drift}$ と $I^0_{drift}$ は、それぞれ $E_g = 0$ ,  $V_{int} = 0$  の時の電流 を表す。

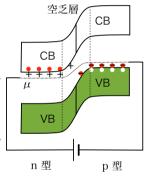

図8に、p-n 接合に逆バイアスを加えた場合の様子を示

## p-n 接合ダイオード:逆バイアス動作

す。電荷担体から見た p-n 接合の障壁が外部電位分だけ増 大するため、電流は $e^{-e(V_{\text{int}}+V_{\text{ext}})/k_{\text{B}}T}$ の因子だけ抑制され、  $V_{\text{ext}} >> V_{\text{int}}$  では  $I = -I_{\text{drift}}$  のみになる。一方、空乏層は誘 電体として働き、その幅は外部ポテンシャルの平方根に比 例して広がるので、電圧可変キャパシターとして動作させ ることが出来る:  $V_{\text{ext}} >> V_{\text{int}}$  の場合、キャパシタンス Cは、 $\rho = eN_A$  を用いて、

$C(V_{\text{ext}}) = \epsilon S/W \approx \epsilon S/(4\epsilon V_{\text{ext}}/\rho)^{1/2} = S(\epsilon e N_A/4)^{1/2} V_{\text{ext}}^{-1/2}$  (10) で与えられる。外部電圧により制御可能なキャパシタであ ることから、バリキャップ(可変容量ダイオード:バリア ブル・キャパシタンス・ダイオード)とも呼ばれる。

図7 界面の電子とホールが再 結合して残った正負電荷が作る

図8 p-n 接合ダイオード に逆バイアスを加えた場合 の動作。

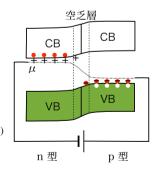

図9 p-n 接合ダイオード に順バイアスを加えた場合 の動作。

09/12/15

### p-n 接合ダイオード: 順バイアス動作

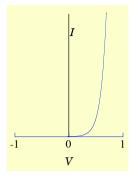

図9に、p-n 接合に順バイアスを加えた場合の様子を示 す。外部電位により、ほとんどの内蔵電位が打ち消され、不 純物による電荷担体が接合面を通してほぼ自由に行き来でき るため、p-n 接合ダイオードを流れる電流は、図10のように 外部電位 Vext の指数関数で変化することが期待される。

ダイオード電流は、拡散電流  $I_{\text{diff}}$  とドリフト電流  $I_{\text{drift}}$  の和 で表せる:

$I(V_{\rm ext}) = I_{\rm diff}(V_{\rm ext}) + I_{\rm drift} = I^0_{\rm diff} \, e^{-e(V_{\rm int} - V_{\rm ext})/k_{\rm B}T} - I^0_{\rm drift} \, e^{-E_g/2k_{\rm B}T}.$ (9) 式を代入し、 $I_0 = I_{drift}$  と置くと、図10に示す  $I(V_{\text{ext}}) = I_0 \left( e^{eV_{\text{ext}}/k_BT} - 1 \right)$

が得られる。

逆バイアスにした場合の漏れ電流は、ボルツマン因 子  $e^{-E_g/k_BT}$  の確率で起こる電子-ホール対のドリフト電 流  $I_{drift}$  である。従って、漏れ電流  $I_0$  はエネルギー ギャップ  $E_g$  の大きさで決まる (Ge:  $E_g \approx 0.66$  eV:  $I_0 =$ 数  $\mu$ A、Si:  $E_{\sigma} \approx 1.1$  eV:  $I_0 =$ 数 nA 以下)。

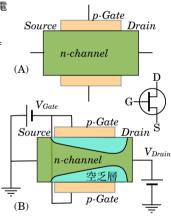

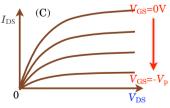

## 接合ゲート電界効果トランジスタ (J-FET)

p-n 接合に逆バイアスを印加すると空乏層が拡大す る。空乏層は電荷担体を持たないため、絶縁層を形 成しており、その幅の制御を通じて、ドープした半導 体のチャネル抵抗値を外部電圧により制御する J-FET 素子が構成される。

図11(A) が J-FET の構造を示す。本体は濃くドー = プされた n-型半導体で、FET の電流の主な通り道に なる。その両側に p-型半導体のゲート (門) 電極が付 けられている。(B) は印加電圧の回路図で、主な電子 の供給源であるソース(源)とドレイン(排出路)間に 電圧 $V_{DS}$ を印加する。p-型ゲートに逆バイアスを加え ると、図8の場合のように、ゲートと p-channel の 境界領域の空乏層が成長し、電流路を塞いでいく。 ドレイン電極に近い部分はゲートードレイン間の電 位差  $V_{\rm CD}$  が大きいために空乏層も広く、ソース側は 接地電位に近く $V_{GS}$ も小さくなり、空乏層は狭い。 ゲート電圧を上げていくと、ドレイン近くでは、遂

図10 p-n 接合ダイ オードを流れる指数関数 的な電流。正の電位差が 順バイアスに対応する。

J-FET の電流一電圧特性

図11 p-n 接合型 FET の構 造 (A)、印加電圧 (B)、電流一 電圧特性 (C)。

には n-channel の電流路の全幅が空乏層になり(その時のゲート電圧をピンチオフ電圧  $V_n$ と呼ぶ)、 $I_{DS}$  はゼロになる。その様子を図11(C)に示す。

この様子は、水路 (channel) を水門 (Gate) で閉じるイメージに近い。 Vps が小さい間 はほぼ  $I_{\rm DS} \propto V_{\rm DS}$  の関係が成り立ち、 $V_{\rm GS}$  で制御が可能な「可変抵抗」として動作する。

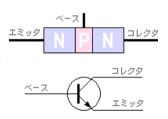

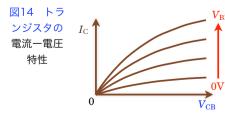

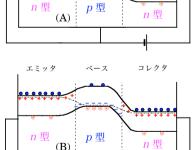

## トランジスタ

J-FET は、空乏層により抵抗値を制御したが、トランジスタは内蔵(障壁)電位を ベース電位により制御し、エミッターコレクタ間の電流を制御する。

図 1 2 に n-p-n 型トランジスタの構造を示す。 2 つの n-型半導体で、なるべく薄くした p-型半導体をサンド イッチした構造で、図13(A) にベース電圧がゼロの時の エネルギー準位を示す。電子放射源のエミッタと収集電 極のコレクタはドープした n-型半導体で、キャリアは電 子である。コレクタを正にバイアスしてポテンシャルを 下げているので、エミッタから見るとコレクタのエネル ギーは低く、ベースが無ければエミッタからコレクタに ドリフト電子流が起こる。しかし、エミッターベース間 の n-p 接合の障壁電位を乗り越えなければ電流は流れな い。そこで、ベース電位をエミッタに対して正にバイア

図12 n-p-n 型 トランジ スタの構造と回路記号。

コレクタ

エミッタ

ス(ダイオードの順バイアス)すると図9に見 るように、障壁電位がバイアス分だけ下がり、 エミッタの電子が容易に熱励起されベースに流 れ込む。その一部はベース電流になるが、ほと んどの電子は薄いベースを通過してコレクタに 流れこむ。ベース電流の割合は、ベースの p-型 不純物濃度やその厚みによって決まる。通常は 1/h<sub>FE</sub> (h<sub>FE</sub> ≈100 程度) になり、 h<sub>FE</sub> を電流増幅 率と呼ぶ。世界で最初にブラッテン、バー ディーン、ショックレーにより作られたトラン

ジスタは、Ge の n-p-n 型である。

図13 n-p-n 型 トランジスタの動 作原理。(A) ベース電圧がゼロの時。 (B) ベース電位を印加したとき。

09/12/15